연세소식

-

[연구 프론티어] 임성일 교수팀, 고성능 음의 정전용량 트랜지스터 개발

연세대학교 홍보팀 / news@yonsei.ac.kr2023-04-14 -

임성일 교수팀, 고성능 음의 정전용량 트랜지스터 개발

강유전성 고분자 극박막 결정 기술 사용

신소재 강유전 물질로 이력현상 없는 저전력 소자 기술 혁신 이끈다

이과대학 물리학과 임성일 교수 연구팀은 수 나노미터(㎚)에 해당하는 강유전성 고분자 극박막 결정 기술을 사용해 2차원 층상형 나노소재인 이황화몰리브덴(MoS2)을 채널로 한 음의 정전용량 트랜지스터를 개발했다.

기존 반도체 소자는 고도의 집적화가 이뤄지는 과정에서 전력 소모가 증가해 이를 막기 위한 다양한 연구가 진행돼 왔다. 하지만 문턱전압이하 스윙(Subthreshold swing; 이하 S.S.)이 60mV/dec보다 낮아질 수 없다는 물리적 한계에 부딪혀 새로운 돌파구가 필요한 시점이다. S.S.는 작은 입력 전압 차이로도 충분한 출력 신호를 생성할 수 있는 트랜지스터의 민감도를 의미하는데, 일반적으로 이 값이 작을수록 더 효율적인 전력 소모가 가능하다. 이에 많은 차세대 기술들이 제안되고 있는데, 그중 하나가 ‘음의 정전용량 현상’을 적용하는 기술이다.

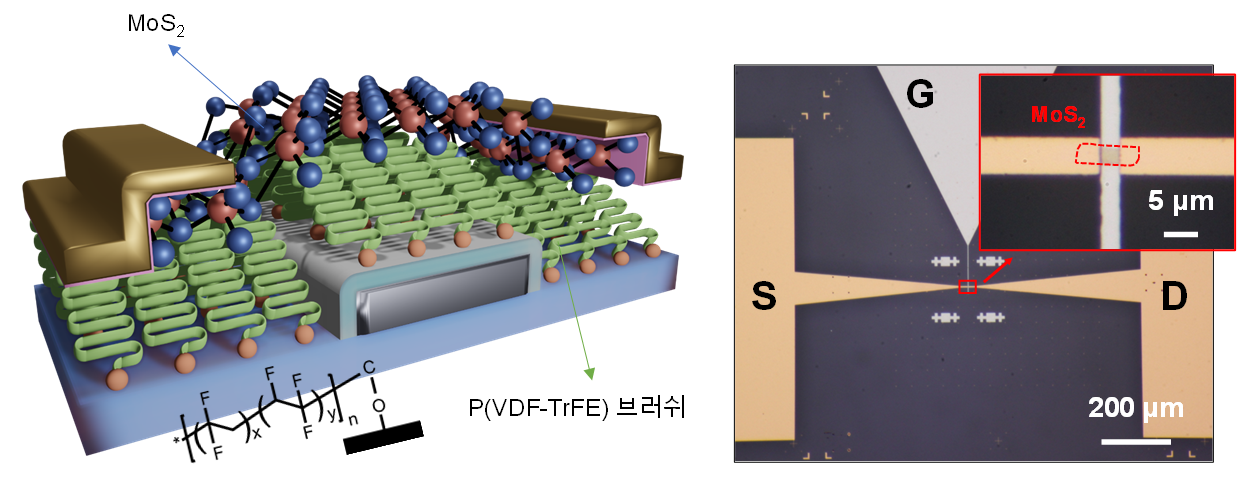

[그림 1. P(VDF-TrFE) 극박막 결정 유전체와 2차원 이황화몰리브덴(MoS2) 채널을 적용한 음의 정전용량 트랜지스터의 3차원 모식도(좌) 및 현미경 사진(우)]

[그림 1. P(VDF-TrFE) 극박막 결정 유전체와 2차원 이황화몰리브덴(MoS2) 채널을 적용한 음의 정전용량 트랜지스터의 3차원 모식도(좌) 및 현미경 사진(우)]음의 정전용량 현상은 인가된 전압이 증가하면 유전체에 축전된 전하량이 감소하는 것을 의미한다. 마치 책상을 기울일수록 구슬이 점점 굴러떨어지는 것이 아니라 되려 높은 곳으로 올라가는 것과 같은 현상으로, 얼핏 불가능한 물리적 현상처럼 보이지만 유전체와 강유전체를 적절히 조합한다면 가능하다. 이 현상을 이용한 트랜지스터는 인가하는 전압을 내부적으로 일부 증폭시키기 때문에 상대적으로 낮은 동작 전압에서도 구동이 가능해 전력 소모를 줄일 수 있다.

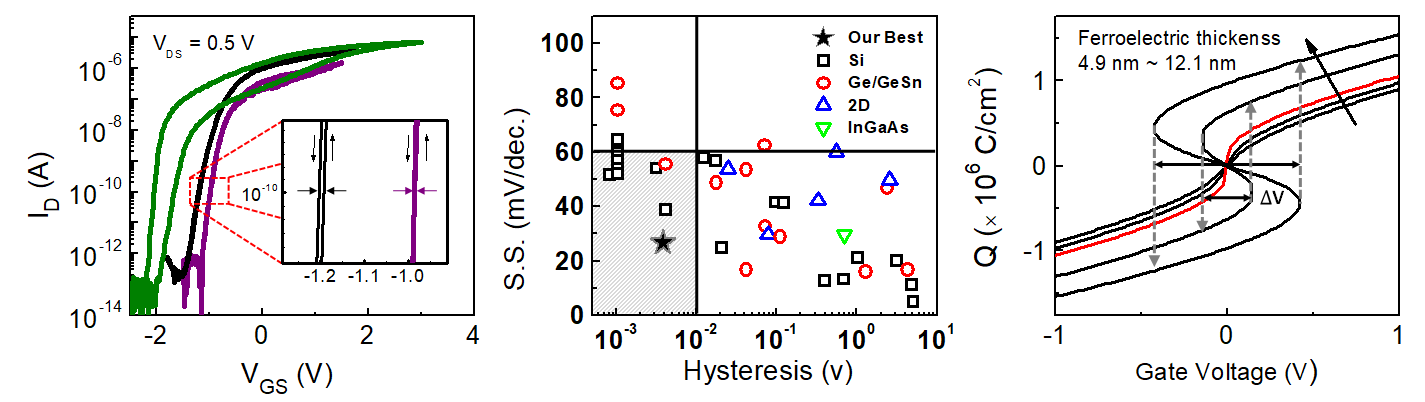

그러나 음의 정전용량 트랜지스터는 구동 전압의 이력현상(Hysteresis)을 항상 보여주는 문제가 있다. 이력현상은 소자의 안정성을 보여주는 중요한 지표로, 연구팀은 알루미늄 산화물 유전체와 P(VDF-TrFE) 강유전체 극박막의 상대적 두께 비율을 최초로 연구해 이력현상을 제거했으며, 이를 바탕으로 MoS2 트랜지스터의 S.S.를 이론적 한계값인 60mV/dec보다 획기적으로 낮은 28mV/dec로 감소시켰다.

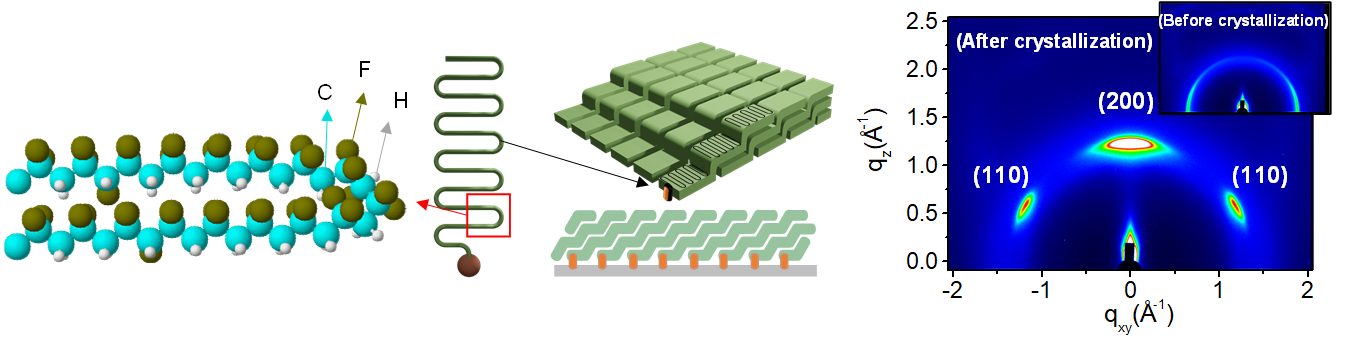

[그림 2. (왼쪽부터) P(VDF-TrFE) 고분자 결정구조 모형, 극박막의 2&3차원 모식도, 그레이징 입사 광각 X선 산란(GIWAXs) 결과]

연구팀은 이에 그치지 않고 트랜지스터를 이론적, 실험적으로 분석하는 방법을 개발해 제안했다. 이전까지는 음의 정전용량 트랜지스터에 관한 연구가 제한적이었으나 연구팀이 이를 평가하고 연구하는 방법을 제시하면서, 저전력 소자에 관한 연구가 한층 더 가속화될 것으로 기대된다.

이번 연구에서 사용된 강유전성 유기물은 미세공정에 의해 녹아 없어지기 때문에 집적화가 필요한 반도체 시장에서 달갑지 않은 재료이다. 연구팀은 유기물인 강유전성 고분자 극박막을 기판과 화학결합시켜 미세공정 문제와 고온에서의 결정성 분해 문제를 해결했다. 이를 통해 유기물질의 집적소자공정 적용 가능성을 확인했다.

[그림 3. (왼쪽부터) 음의 정전용량 트랜지스터 전류-전압 곡선, 기존 연구들과의 비교 그래프, 이력현상 제어를 위한 이론적 분석 시뮬레이션]

임성일 교수는 “개발한 음의 정전용량 트랜지스터는 현재 고도의 집적화가 요구되는 반도체 시장에서 중요한 발전을 이끌어 낼 새로운 기술”이라며 “낮은 S.S.와 극소의 이력현상을 가지는 등 트랜지스터의 산업화에 필요한 중요한 기술적 요건을 충족하며 전력 소모를 줄일 수 있어, 반도체 소자의 개발 방향을 제시하고 지속 가능한 발전을 이끌어 내는 계기가 될 것”이라고 연구의 의의를 전했다.

이 연구는 과학기술정보통신부 선도연구센터지원사업(SRC)과 연세시그니처연구클러스터사업의 지원을 받아 수행됐으며, 조현민 박사가 제1저자로, 임성일 교수가 제1교신저자로, 류두열 교수가 참여저자로, 김관표 교수, 단국대 박지훈 교수가 제2교신저자로 참여했다. 연구 결과는 재료과학 분야 세계적 권위지인 ‘어드밴스드 머티리얼즈(Advanced Materials)’에 4월 13일 온라인 게재됐다.

논문정보

● 논문제목: 5 nm-ultrathin crystalline ferroelectric P(VDF-TrFE)-brush tuned for hysteresis-free sub-60 mV/dec negative capacitance transistors

● 논문주소: https://doi.org/10.1002/adma.202300478

용어설명

● 2차원 층상형 나노소재: 원자들이 단일 원자층 두께(약 1㎚=10억 분의 1m)를 가지고 2차원 평면에서 결정구조를 이루고 있는 저차원 나노소재로, 원자층 사이에 약한 반데르발스 힘으로 결합돼 층상형 구조를 이룬다.

● Subthreshold Swing (S.S.) : 트랜지스터를 얼마나 신속하게 켜고 끌 수 있는지를 판단할 수 있는 평가 요소 중 하나이다. 보통 전류가 10배 증가할 때 얼마나 전압을 증가시켰는지로 정의된다. S.S.를 결정짓는 요소는 크게 두 가지가 있는데, 첫 번째로는 외부에서 인가되는 게이트 전압에 채널로 사용되는 반도체 물질이 얼마나 민감히 반응하는지가 중요하다. 두 번째로는 그 게이트 전압이 얼마나 효과적으로 반도체 물질에 전달되는지가 중요하다. 이는 게이트 전극과 반도체 채널 물질 사이에 있는 게이트 유전체의 정전용량에 대한 것이다. 일반적으로 S.S.는 이 두 가지 요소의 곱으로 나타나며, 최소값은 60mV/dec가 된다.

● 이력현상(hysteresis): 게이트 전압이 변화함에 따라 출력 전류 곡선이 이전 상태와 다른 값을 가지는 현상으로, 소자의 안정성을 보여주는 중요한 지표가 된다. 이력현상이 심한 경우에는 소자를 꺼진 상태에서 켰다가 다시 끄려고 해도 안 꺼지는 현상이 생길 수 있다. 이 현상이 생기는 데는 매우 다양한 원인이 있는데, 일반적으로 매번 동일한 성능을 보여줘야 하는 소자의 경우에는 이력현상이 작을수록 유리하다. 반면 이러한 이력현상의 특성을 일부러 극대화시켜 메모리 소자로 활용할 수도 있다.

● Boltzmann’s tyranny : S.S.는 일반적으로 60mV/dec보다 낮아질 수 없다. Boltzmann’s tyranny는 이러한 한계를 의미한다. 일반적인 게이트 유전체를 사용한다면 S.S.를 물리학적으로 60mV/dec보다 낮출 수 없기 때문에 이 한계를 극복하기 위해 학계에서는 다양한 방법을 시도해 왔다. 그러한 기술 중 하나가 음의 정전용량 효과를 이용하는 방법이다.

- vol. 전체

- vol. 636

- vol. 635

- vol. 634

- vol. 633

- vol. 632

- vol. 631

- vol. 630

- vol. 629

- vol. 628

- vol. 627

- vol. 626

- vol. 625

- vol. 624

- vol. 623

- vol. 622

- vol. 621

- vol. 620

- vol. 619

- vol. 618

- vol. 617

- vol. 616

- vol. 615

- vol. 614

- vol. 613

- vol. 612

- vol. 611

- vol. 610

- vol. 609

- vol. 608

- vol. 607

- vol. 606

- vol. 605

- vol. 604

- vol. 603

- vol. 602

- vol. 601

- vol. 600

- vol. 599

- vol. 598

- vol. 597

- vol. 596

- vol. 595

- vol. 594

- vol. 593

- vol. 592

- vol. 591

- vol. 590

- vol. 589

- vol. 587

- vol. 586

- vol. 585

- vol. 584

- vol. 583

- vol. 582

- vol. 581

- vol. 580

- vol. 579

- vol. 578

- vol. 577

- vol. 576

- vol. 575

- vol. 574

- vol. 573

- vol. 572

- vol. 571

- vol. 570

- vol. 569

- vol. 568

- vol. 567

- vol. 566

- vol. 565

- vol. 564

- vol. 563

- vol. 562

- vol. 561

- vol. 560

- vol. 559

- vol. 558

- vol. 557

- vol. 556

- vol. 555

- vol. 554

- vol. 553

- vol. 552

- vol. 551

- vol. 550

- vol. 549

- vol. 548

- vol. 547

- vol. 546

- vol. 545

- vol. 544

- vol. 543

- vol. 542

- vol. 541

- vol. 540

- vol. 539

- vol. 538

- vol. 537

- vol. 536

- vol. 535

- vol. 534

- vol. 533

- vol. 532

- vol. 531

- vol. 530

- vol. 529

- vol. 528

- vol. 527

- vol. 526

- vol. 525

- vol. 524

- vol. 523

- vol. 522

- vol. 521

- vol. 520

- vol. 519

- vol. 518

- vol. 517

- vol. 516

- vol. 515

- vol. 514

- vol. 513

- vol. 512

- vol. 511

- vol. 510

- vol. 509

- vol. 508

- vol. 507

- vol. 506

- vol. 505

- vol. 504

- vol. 503

- vol. 502

- vol. 501

- vol. 500

- vol. 499

- vol. 498

- vol. 497

- vol. 496

- vol. 495

- vol. 494

- vol. 493

- vol. 492

- vol. 491

- vol. 490

- vol. 489

- vol. 488

- vol. 487

- vol. 486

- vol. 485

- vol. 484

- vol. 483

- vol. 482

- vol. 481

- vol. 480

- vol. 479

- vol. 478

- vol. 477

- vol. 476

- vol. 475

- vol. 474

- vol. 473

- vol. 472

- vol. 471

- vol. 470

- vol. 469

- vol. 468

- vol. 467

- vol. 466

- vol. 465

- vol. 464

- vol. 463

- vol. 462

- vol. 461

- vol. 460

- vol. 459

- vol. 458

- vol. 457

- vol. 456

- vol. 455

- vol. 454

- vol. 453

- vol. 452

- vol. 451

- vol. 450

- vol. 449

- vol. 448

- vol. 447

- vol. 446

- vol. 445

- vol. 444

- vol. 443

- vol. 442

- vol. 441

- vol. 440

- vol. 439

- vol. 438

- vol. 437

- vol. 436

- vol. 435

- vol. 434

- vol. 433

- vol. 432

- vol. 431

- vol. 430

- vol. 429

- vol. 428

- vol. 427

- vol. 426

- vol. 425

- vol. 424

- vol. 423

- vol. 422

- vol. 421

- vol. 420

- vol. 419

- vol. 418

- vol. 417

- vol. 416

- vol. 415

- vol. 414

- vol. 413

- vol. 412

- vol. 411

- vol. 410

- vol. 409

- vol. 408

- vol. 407

- vol. 406

- vol. 405

- vol. 404

- vol. 403

- vol. 402

- vol. 401

- vol. 400

- vol. 399

- vol. 398

- vol. 397

- vol. 396

- vol. 395

- vol. 394

- vol. 393

- vol. 392

- vol. 391

- vol. 390

- vol. 389

- vol. 388

- vol. 387

- vol. 386

- vol. 385

- vol. 384

- vol. 383

- vol. 382

- vol. 381

- vol. 380

- vol. 379

- vol. 378

- vol. 377

- vol. 376

- vol. 375

- vol. 374

- vol. 373

- vol. 372

- vol. 371

- vol. 370

- vol. 369

- vol. 368

- vol. 367

- vol. 366

- vol. 365

- vol. 364

- vol. 363

- vol. 362

- vol. 361

- vol. 360

- vol. 359

- vol. 358

- vol. 357

- vol. 356

- vol. 355

- vol. 354

- vol. 353

- vol. 352

- vol. 351

- vol. 350

- vol. 349

- vol. 348

- vol. 347

- vol. 346

- vol. 345

- vol. 344

- vol. 343

- vol. 342

- vol. 341

- vol. 340

- vol. 339

- vol. 338

- vol. 337

- vol. 336

- vol. 335

- vol. 334

- vol. 333

- vol. 332

- vol. 331

- vol. 330

- vol. 329

- vol. 328

- vol. 327

- vol. 326

- vol. 325

- vol. 324

- vol. 323

- vol. 322

- vol. 321

- vol. 320

- vol. 319

- vol. 318

- vol. 317

- vol. 316

- vol. 315

- vol. 314

- vol. 313

- vol. 312

- vol. 311

- vol. 310

- vol. 309

- vol. 308

- vol. 307

- vol. 306

- vol. 305

- vol. 304

- vol. 303

- vol. 302

- vol. 301

- vol. 300

- vol. 299

- vol. 298

- vol. 297

- vol. 296

- vol. 295

- vol. 294

- vol. 293

- vol. 292

- vol. 291

- vol. 290

- vol. 289

- vol. 288

- vol. 287

- vol. 286

- vol. 285

- vol. 284

- vol. 283

- vol. 282

- vol. 281

- vol. 280

- vol. 279

- vol. 278

- vol. 277

- vol. 276

- vol. 275

- vol. 274

- vol. 273

- vol. 272

- vol. 271

- vol. 270

- vol. 269

- vol. 268

- vol. 267

- vol. 266

- vol. 265

- vol. 264

- vol. 263

- vol. 262

- vol. 261

- vol. 260

- vol. 259

- vol. 258

- vol. 257

- vol. 256

- vol. 255

- vol. 254

- vol. 253

- vol. 252

- vol. 251

- vol. 250

- vol. 249

- vol. 248

- vol. 247

- vol. 246

- vol. 245

- vol. 244

- vol. 243

- vol. 242

- vol. 241

- vol. 240

- vol. 239

- vol. 238

- vol. 237

- vol. 236

- vol. 235

- vol. 234

- vol. 233

- vol. 232

- vol. 231

- vol. 230

- vol. 229

- vol. 228

- vol. 227

- vol. 226

- vol. 225

- vol. 224

- vol. 223

- vol. 222

- vol. 221

- vol. 220

- vol. 219

- vol. 218

- vol. 217

- vol. 216

- vol. 215

- vol. 214

- vol. 213

- vol. 212

- vol. 211

- vol. 210

- vol. 209

- vol. 208

- vol. 207

- vol. 206

- vol. 205

- vol. 204

- vol. 203

- vol. 202

- vol. 201

- vol. 189

- vol. 188

- vol. 187

- vol. 186

- vol. 185

- vol. 184

- vol. 183

- vol. 182

- vol. 181

- vol. 180

- vol. 179

- vol. 178

- vol. 177

- vol. 176

- vol. 175

- vol. 174

- vol. 173

- vol. 172

- vol. 171

- vol. 170

- vol. 169

- vol. 168

- vol. 167

- vol. 166

- vol. 165

- vol. 164

- vol. 163

- vol. 162

- vol. 161

- vol. 160

- vol. 159

- vol. 158

- vol. 157

- vol. 156

- vol. 155

- vol. 154

- vol. 153

- vol. 152

- vol. 151

- 전체 글 보기

- 연세 뉴스

- 여기 연세인

- 연세 사랑

- 화제의 인물

- Academia

- 연구 프론티어

- 특별기획

- LearnUs 이달의 강의

- 기관 탐방

- 신촌캠퍼스 소식

- 의료원 소식

- 미래캠퍼스 소식

- 국제캠퍼스 소식

- 신간 안내

- 동정

연세소식 신청방법

아래 신청서를 작성 후 news@yonsei.ac.kr로 보내주세요신청서 다운로드